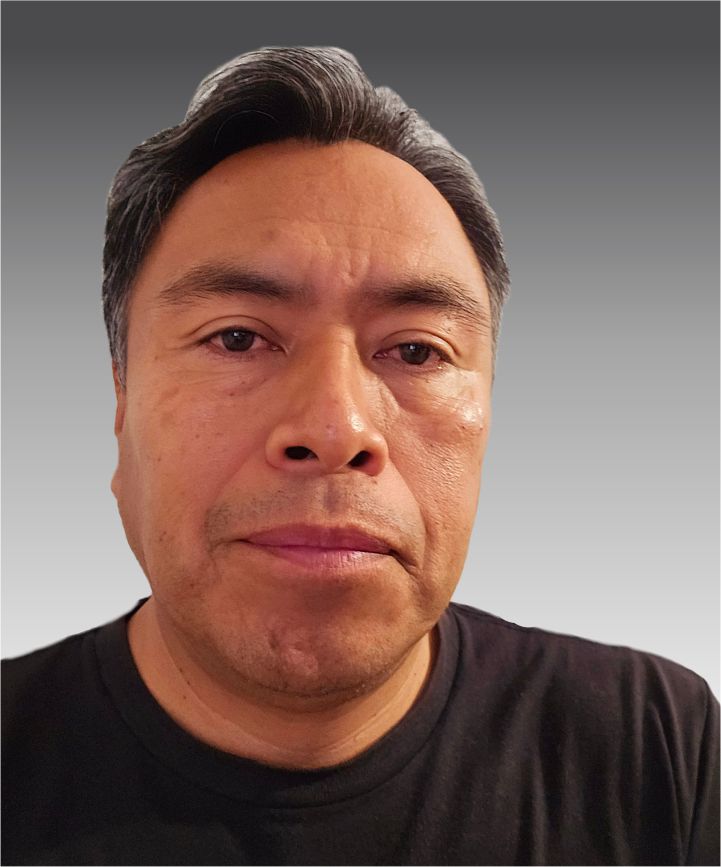

Dr. Esteban Tlelo Cuautle

SNI NIVEL 3

Correo Electrónico: etlelo@inaoep.mx

Teléfono: +52 222 266 31 00 ext. 1404

Oficina: 1404

Información Curricular

Doctorado obtenido en: INAOE, en 2000.

Título de Tesis: "Desarrollo de un Método de Polarización para Circuitos Integrados Analógicos

Maestría en Ciencias obtenido en: INAOE, en 1995.

Licenciatura: Instituto Tecnológico de Puebla, en 1993.

Líneas de investigación

-

Diseño y optimización de circuitos y sistemas integrados.

-

Aplicaciones de sistemas caóticos en IoT, criptografía y seguridad.

-

Circuitos y sistemas de orden fraccionario.

-

Implementationes de circuitos y sistemas no-lineales en hardware embebido.

Proyectos:

-

New optimization methodologies of integrated circuits and systems of fractional-order with applications to IoT, cryptography and security.

Últimas Tesis Dirigidas:

Sandra Huerta Moro, Control de orden entero/fraccionario para un convertidor CD-CD tipo reductor, INAOE, 2025

Carlos Alejandro Velázquez Morales, Optimización de OTAs para mejorar el diseño CMOS de una neurona LIF basada en memristor, INAOE, 2025

Astrid Maritza González Zapata, Métodos de Aprendizaje Automático para la Predicción de Series Temporales Caóticas, INAOE, 2024

Perla Rubí Castañeda Aviña, Optimización de VCO en Tecnología CMOS Aplicando Metaheurísticas, INAOE, 2023

Martín Alejandro Valencia Ponce, Optimización de circuitos integrados analógicos aplicando metaheurísticas de muchos objetivos, INAOE, 2022

Reconocimientos:

Ganador del Premio Estatal de Ciencia y Tecnología "Luis Rivera Terrazas" 2024. Categoría de Investigación en Ciencias Básicas y Humanidades, Sección I: Física-Matemáticas, Ciencias de la Tierra e Ingenierías.

Considerado dentro de los 10 mejores: Best Electronics and Electrical Engineering Scientists in Mexico

Libros:

Luis Gerardo de la Fraga, José David Rodríguez-Muñoz, Esteban Tlelo-Cuautle, Random Number Generators: Verilog Description, Hardware Implementation and Applications, Springer, eBook ISBN 978-3-031-82865-2 , Hardcover ISBN978-3-031-82864-5, 195 pages, Abril 2025. https://doi.org/10.1007/978-3-031-82865-2

Esteban Tlelo-Cuautle, Luis Gerardo de la Fraga, Omar Guillén-Fernández, Alejandro Silva-Juárez, Optimization of integer/fractional order chaotic systems by metaheuristics and their electronic realization, CRC Press, Taylor & Francis Group, ISBN: 978-0367486686, 266 pages, May 2021. DOI: 10.1201/9781003042181

Esteban Tlelo-Cuautle, Ana Dalia Pano-Azucena, Omar Guillén-Fernández, Alejandro Silva-Juárez, Analog/Digital Implementation of Fractional Order Chaotic Circuits and Applications, Springer, ISBN: 978-3-030-31249-7, eISBN: 978-3-030-31250-3, 214 pages, 2020. DOI: 10.1007/978-3-030-31250-3

Esteban Tlelo-Cuautle, Luis Gerardo de la Fraga, José de Jesús Rangel Magdaleno, Engineering Applications of FPGAs: Chaotic Systems, Artificial Neural Networks, Random Number Generators, and Secure Communication Systems, Springer, ISBN: 978-3-319-34113-2, eISBN: 978-3-319-34115-6, 230 pages, 2016. DOI: 10.1007/978-3-319-34115-6

G. Shi, S. X.-D. Tan, E. Tlelo-Cuautle, Advanced Symbolic Analysis for VLSI Systems-Methods and Applications, Springer, ISBN: 978-1-4939-1102-8,eISBN: 978-1-4939-1103-5, 300 pages, July 2014. DOI: DOI 10.1007/978-1-4939-1103-5

J.M. Muñoz-Pacheco, E. Tlelo-Cuautle, Electronic design automation of multi-scroll chaos generators, Bentham Sciences Publishers Ltd., eISBN: 978-1-60805-165-6, 96 pages, 2010. doi:10.2174/97816080516561100101

Publicaciones Recientes:

-

Joselyn Mayte Fernández-Martínez, Gregorio Zamora-Mejia, Esteban Tlelo-Cuautle, Alejandro Díaz-Sánchez, A Low-Power, Highly Tunable Ring Oscillator Architecture Based on a QFGT-Modified Maneatis Cell, International Journal of Circuit Theory And Applications, eISSN 1097-007X, March 2026. https://doi.org/10.1002/cta.70192

-

Arnaud Nanfak, Jean de Dieu Nkapkop, Kotadai Zourmba, Joseph Mvogo Ngono, Maria Fernanda Moreno-Lopez, Esteban Tlelo-Cuautle, Monica-Elena Borda, Joseph Yves Effa, Dynamic analysis and FPGA implementation of a 2D fractional sine-cosine map for image encryption using bit-level permutation and genetic algorithm, Mathematics and Computers in Simulation, vol. 240, no. 1, pp. 105–136, ISSN: 0378-4754, eISSN 1872-7166, February 2026. https://doi.org/10.1016/j.matcom.2025.07.022

-

Sandra Huerta-Moro, Esteban Tlelo-Cuautle, Parasitic Resistance and Circuit Vari- ation Effects in a DC–DC Buck Converter With Integer/Fractional-Order PID Con- trollers, International Journal of Circuit Theory And Applications, eISSN 1097-007X, January 2026. https://doi.org/10.1002/cta.70088

-

Luis M. López-Jiménez, Esteban Tlelo-Cuautle, Luis F. Cisneros-Sinencio, Alejandro Díaz-Sánchez, Experimental Evaluation of Memristor-Enhanced Analog Oscillators: Relaxation and Wien Bridge Cases, Dynamics, vol. 5, no. 4, Art. 43, pp. 1-13, eISSN 2673-8716, October 2025. https://doi.org/10.3390/dynamics5040043

-

Min Tian, Yingjing Shi, Rui Li, Esteban Tlelo-Cuautle, Rapid Generation of the Shortest Generalized Dubins Path in Forced Landing, International Journal of Applied Mathematics and Computer Science, vol. 35, no. 2, pp. 195–207, eISSN 2083-8492, June 2025. https://doi.org/10.61822/amcs-2025-0014

Página Principal:

https://publons.com/researcher/1487250/esteban-tlelo-cuautle/

Editor en Revistas y Organización de Congresos

Associate Editor in Fractal and Fractional Q1

Associate Editor in International Journal of Circuit Theory and Applications, Q3

Associate Editor in Engineering Applications of Artificial Intelligence Q1

Associate Editor in Integration – the VLSI Journal Q3

Associate Editor in Frontiers of Information Technology & Electronics Engineering (FITEE) Q3

Associate Editor in Electronics Q2

Associate Editor in IEEE Transactions on Circuits and Systems-I: Regular Papers Q2

Co-Chair: EDIESCA 2025 https://sistemasdinamicos.amesdyc.org/p%C3%A1gina-principal/eventos_amesdyc/ediesca_2025

Co-Chair: ICCS 2025 Chengdu, China. http://iccs.org/com.html

Dirección: Luis Enrique Erro # 1, Tonantzintla, Puebla, México C.P. 72840 Teléfono: (222) 266.31.00 Contacto: difusion@inaoep.mx

Esta obra está licenciada bajo una Licencia Creative Commons Atribución-No Comercial-Sin Obras Derivadas 2.5 México